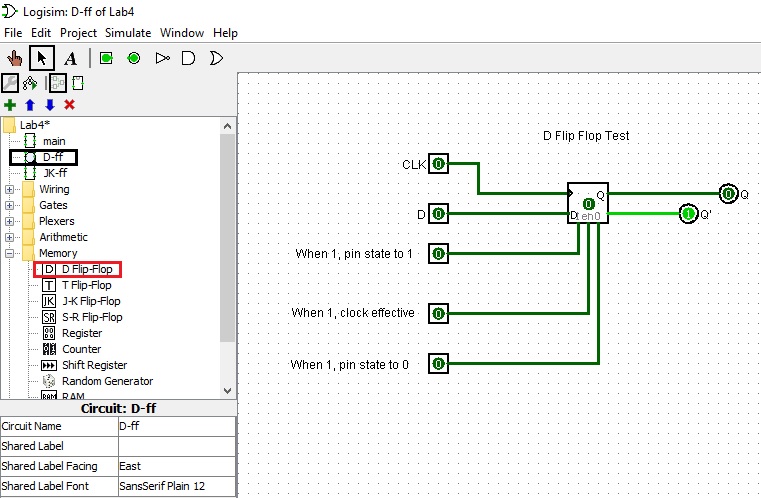

The D flip-flop(shown below) lets the input at D propogate through to Q on the positive going edge of the clock. The present state-next state chart illustrates the behavior of the D flip-flop. Basically Q(t+1) = D, which is the characteristic equation.

Characteristic Table Excitation Table ==================== =================== D Q(t+1) Operation Q(t) Q(t+1) D ==================== =================== 0 0 Reset 0 0 0 -------------------- ------------------- 1 1 Set 0 1 1 ==================== ------------------- 1 0 0 ------------------- 1 1 1 ===================

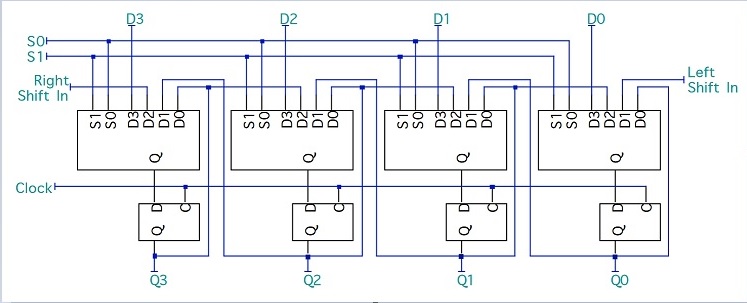

Here is a demonstration of 4-1 Multilexer with four input lines D0, D1, D2, D3 for your reference.

Truth Table of a 4-1 Multiplexer (MUX 4) ======================================== Input Selection Output ---------------------------------------- S1 S0 Q D0 0 0 D0 D1 0 1 D1 D2 1 0 D2 D3 1 1 D3 -----------------------------------------

Select Inputs Function

S1 S0

------------------------

0 0 Store

0 1 Shift left

1 0 shift right

1 1 Load